Neosyn SDK

Professional development environment for modern FPGA engineering. Eclipse-based, vendor-agnostic, and built for engineers who ship.

Why Neosyn SDK?

FPGA development shouldn't require deciphering cryptic HDL or fighting with vendor tools. The Neosyn SDK gives you a modern development environment where you write in Cx—a readable, C-like language—and compile to production-ready Verilog or VHDL.

No more vendor lock-in. Write once, deploy to any FPGA—Intel, Xilinx, Lattice, Microchip. The SDK generates clean, portable HDL that synthesizes efficiently on any platform.

Debug like software, ship like hardware. Cycle-accurate simulation at 10x HDL speed, software-style breakpoints, and waveforms that actually make sense. Git integration that works. Version control where you can see what changed in your design, not just which signal moved in line 8472.

What's Inside

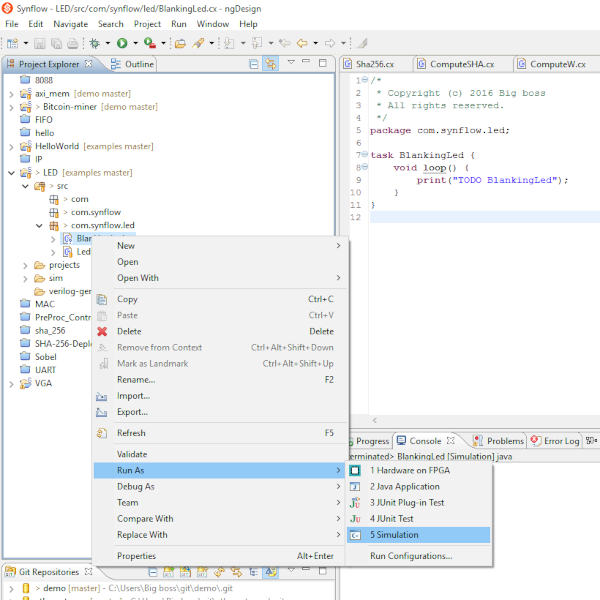

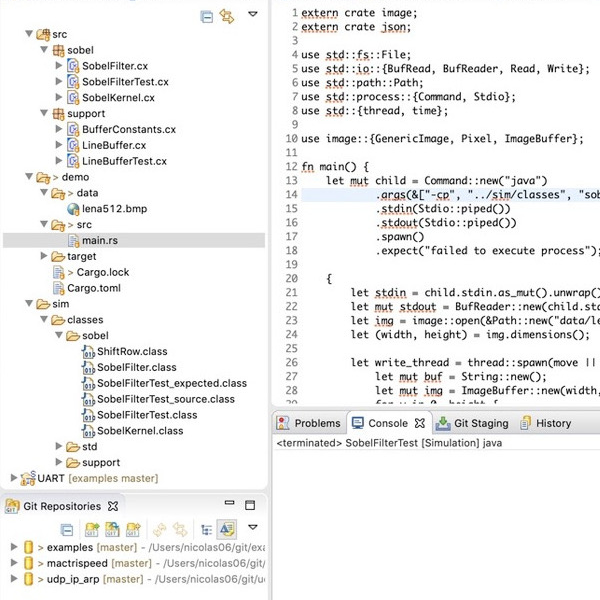

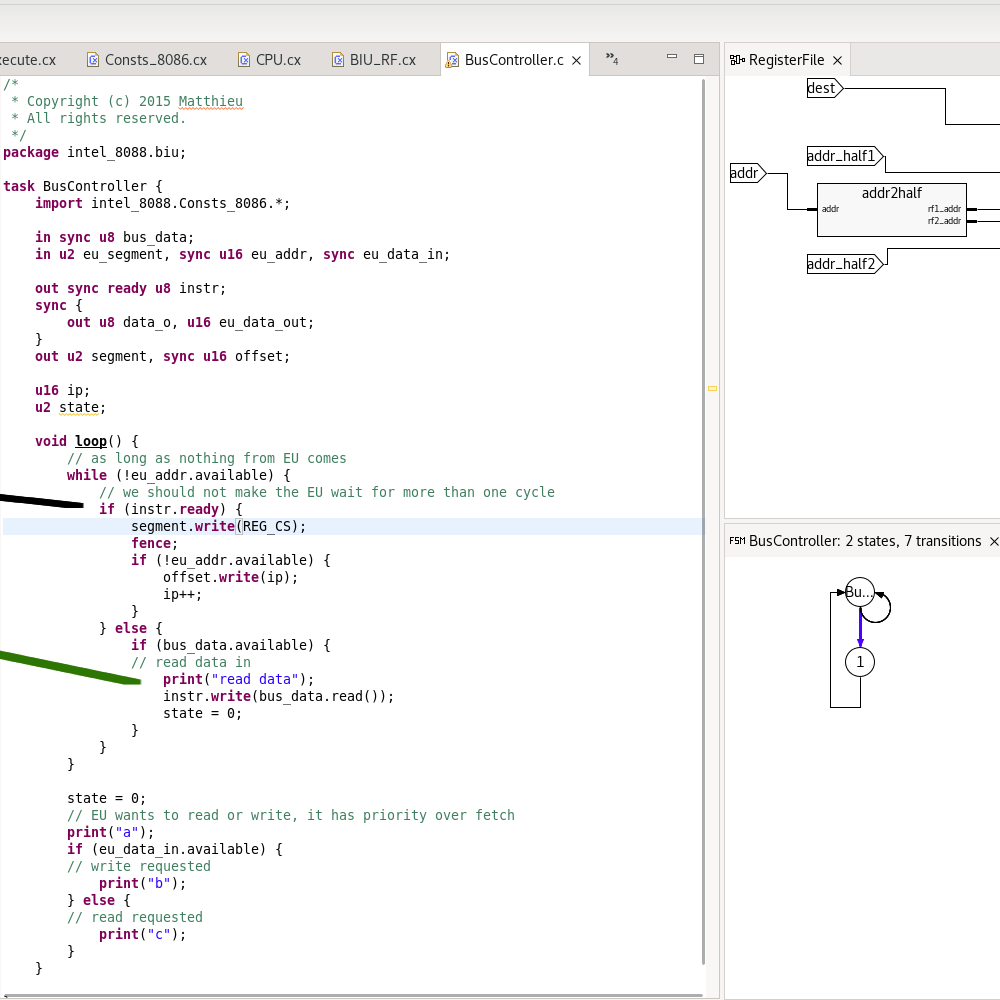

Eclipse-Based IDE

Professional development environment built on Eclipse. Familiar interface, powerful extensions, and the tooling you already know. Code completion, syntax highlighting, and integrated documentation.

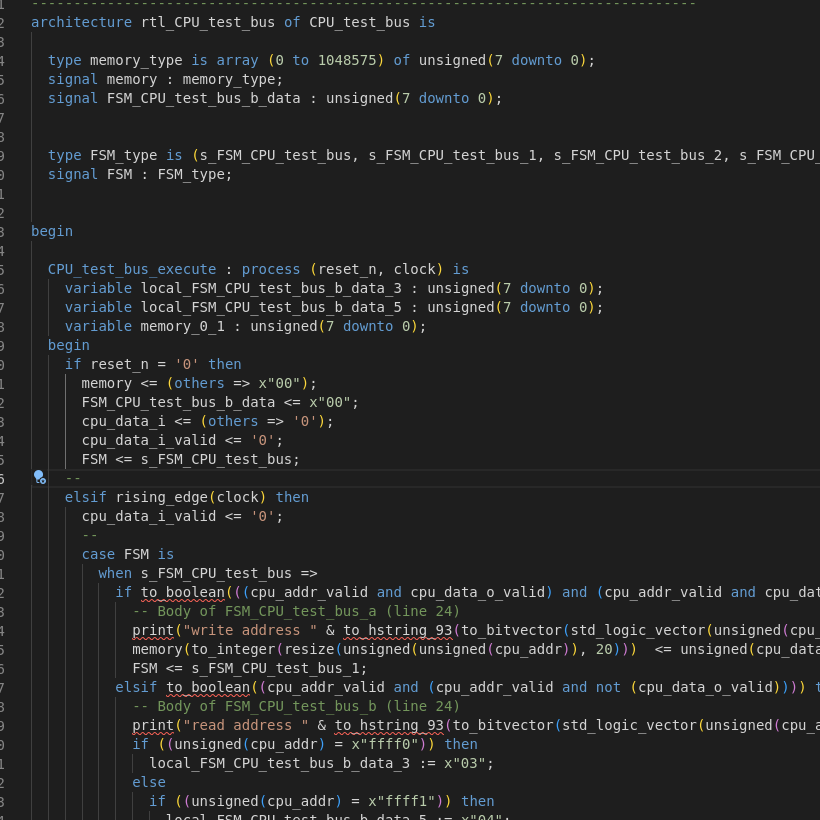

Cx to HDL Compiler

Write in Cx, compile to production-ready Verilog or VHDL. Optimized output that synthesizes efficiently. No hand-editing needed. No vendor-specific quirks. Just clean, portable HDL.

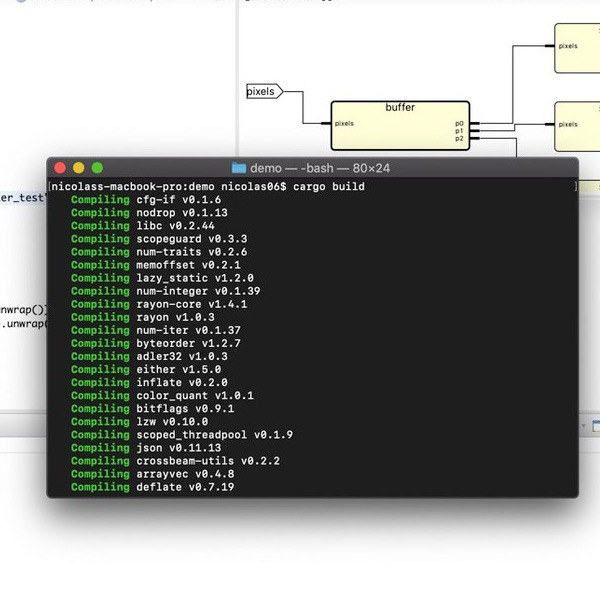

High-Speed Simulator

Cycle-accurate simulation at 10x traditional HDL speed. Debug hardware with software debugging techniques. Waveforms that make sense. Breakpoints that work. No more grep'ing VCD files.

Version Control Integration

First-class Git integration. Diff Cx code like you diff software. Meaningful version history. No more "which signal changed in line 8472 of the VHDL?" Just see what actually changed in your design.

IP Core Libraries

Curated IP core libraries for common functions. UART, SPI, I2C, memory controllers, video processing. Open source Cx code you can read, modify, and actually understand. Build on proven blocks.

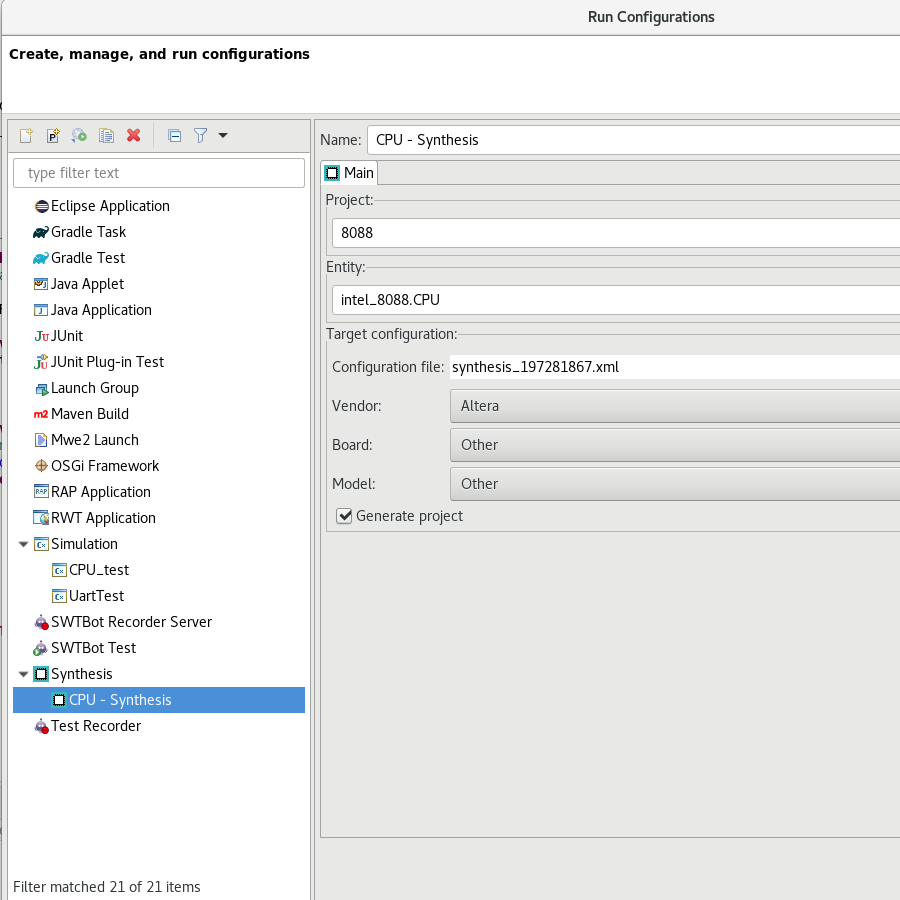

Vendor-Agnostic Workflow

One SDK. Any FPGA. Intel, Xilinx, Lattice, Microchip—doesn't matter. Generate vendor-specific constraints automatically. No rewriting. No tool lock-in. Your design, your choice of silicon.

System Requirements

Windows

Windows 10/11

8GB RAM minimum

2GB disk space

macOS

macOS 11+

8GB RAM minimum

2GB disk space

Linux

Ubuntu 20.04+

8GB RAM minimum

2GB disk space

Ready to ship faster?

Start with a 14-day free trial. Full SDK access. Complete documentation. Example projects included.