Hardware development.Redesigned from silicon up.

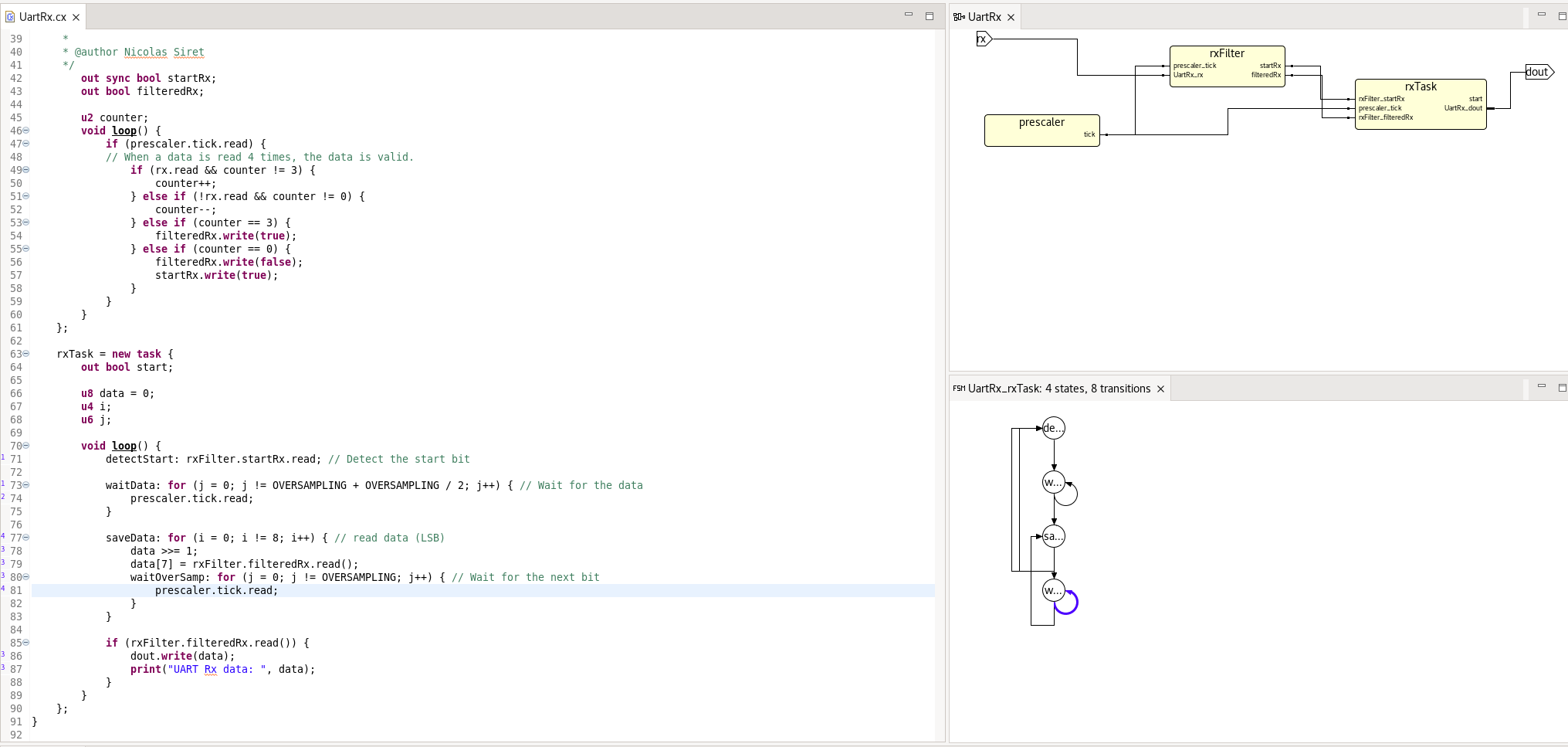

Verilog and VHDL were designed in the 1980s. We built what should have come next: C-like syntax, modern tooling, vendor-agnostic compilation. Write hardware that makes sense.

Three tools. One vision.

Hardware shouldn't be harder than software. We're building the complete stack for modern FPGA development—from language to silicon.

Professional IDE

Neosyn SDK

Eclipse-based development environment. Compile, synthesize, deploy to any FPGA vendor. One tool, no vendor lock-in.

Vendor Agnostic

Works with Intel, Xilinx, Lattice, Microchip. Your code, any FPGA.

10x Faster Development

High-speed simulation. Readable code. Less debugging time.

Production Ready

Clean Verilog/VHDL output. Proven in real projects.

Why Cx beats traditional HDL

Same hardware. Half the code. Zero vendor lock-in.

Traditional HDL (Verilog/VHDL)

Designed in the 1980s for a different era

- Verbose syntax

100+ lines for simple state machines

- Manual state management

Write your own FSMs, counters, protocols

- Slow simulation

Wait hours for large designs to simulate

- Vendor-specific tools

Locked into Intel, Xilinx, or Lattice ecosystems

- Poor tooling

No real IDE support, debugging, or refactoring tools

Cx + Neosyn SDK

Modern hardware development for 2025

- C-like syntax

50% less code. Reads like software. Compiles to HDL.

- Built-in abstractions

Tasks, ports, wait() statements handle complexity

- 10x faster simulation

Cycle-accurate, high-speed simulator included

- Vendor agnostic

One codebase, any FPGA: Intel, Xilinx, Lattice, Microchip

- Professional IDE

Eclipse-based with code completion, debugging, refactoring

Trusted by makers and SMEs

We pride ourselves on building positive relationships with our clients. Check out what everyone is saying about Neosyn.

“ I have developed IP cores using the Neosyn SDK. The network and FSM viewers are very useful features. I am bluffed by the quality of the toolset and the performance I get on my Virtex.“Łukasz Bolda

Building an Ecosystem

Great tools need great hardware. We're partnering with companies who share our vision of making FPGA development accessible to everyone.

Pixilica LLC

Raspberry Pi for FPGAs

Affordable FPGA development boards designed for makers, students, and engineers. No corporate budgets required. No vendor lock-in. Just accessible hardware that works with Neosyn SDK out of the box.

- • Maker-friendly pricing

- • Neosyn SDK ready

- • Open hardware designs

- • Community-driven

Brane Technologies

Heterogeneous Computing for Local AI

Super local AI powered by heterogeneous computing. CPU, GPU, and optional FPGA acceleration in workstation format or board-level solutions. Privacy-first architecture that keeps your data local. No cloud dependencies.

- • Heterogeneous CPU/GPU/FPGA compute

- • Workstation & board formats

- • Local AI inference

- • Privacy-first design

- • Optional FPGA acceleration with Neosyn

The Complete Stack

Pixilica boards + Neosyn tools + Brane AI = The future of accessible FPGA development

Learn More About Our EcosystemBuilt by engineers who got tired of waiting

We've been building FPGA tools for years. This time, we're doing it right.

CONTACT US

Let's talk about your needs, we'd love to hear from you!

Our Location

Startup Lisboa, Rua da Prata 80, 1100-420 Lisboa, Portugal

How Can We Help?

You can also send us an email using our anti-spam email.